Using a serial connection, we can minimize the number of connection wires, minimizing also the skew problem on the connection itself. Such a conversion strategy can be used when we need to connect two different devices like two FPGA, and we need to minimize the connection wires. In this post, we implemented a simple example of a serial to parallel VHDL code. Figure 5 Serial to Parallel ModelSim VHDL simulation ZOOM-IN In Figure5 is highlighted the ZOOM-IN of the serial conversion of the serial pattern “00000010”. Figure 4 Serial to Parallel ModelSim VHDL simulation As clear the serial input to be parallelized is re-serialized in the byte signal. In Figure4 is reported a simulation of the serial to parallel converter VHDL code. It depends on the convention you are using. As a convention, the first serial output bit is the MSB of the input parallel data. In order to realize the test bench, the parallel to serial converter of this post is used.

#PARALLEL TO SERIAL CONVERTER VERILOG CODE CODE#

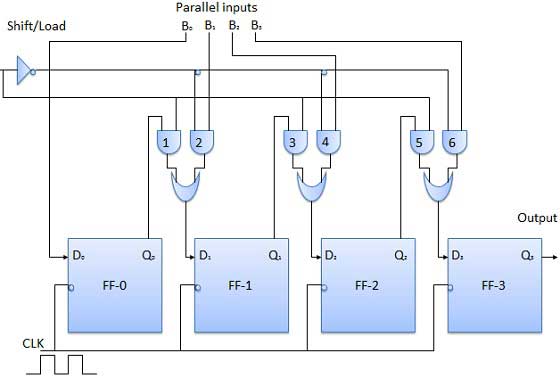

In Figure4 is reported a simulation of the serial to parallel converter VHDL code above. Serial to Parallel converter VHDL simulation resultsįigures below, the clock is set to 10 ns, so 80 ns mean 8 clock cycles. The output parallel data rate is slower than the input serial data rate, so noĮrror condition can occur. Parallel to serial converter in this case no error detection logic is present. Parallel data output and the relative enable pulse. P_serial2parallel : process(i_clk,i_rstb)Īn example of Serial to Parallel converterĬycles the counter enable the parallel output register and provides the Signal r_count : integer range 0 to G_N-1 Signal r_data : std_logic_vector(G_N-1 downto 0) O_data : out std_logic_vector(G_N-1 downto 0)) The parallel output to the module will be available every N clock cycle since N clock cycles are needed to load the shift register that provided the parallel output as in Figure2 Figure 2 Serial to Parallel conversion exampleĪn example of Serial to Parallel converter VHDL code Let assume the parallel data bus of the Serial to Parallel converter to be N bit. Serial to Parallel converter VHDL code example In other words, we will implement the VHDL block in the of the bottom right of Figure1 Figure 1 FPGA connection Parallel vs Serial

#PARALLEL TO SERIAL CONVERTER VERILOG CODE HOW TO#

We will see how to implement the VHDL code for a serial to parallel interface in order to get back the parallel data bus we sent in the transmitter device. In this post, we want to implement the complementary interface of the parallel to serial interface. Many FPGA vendors like Xilinx, Intel/Altera give us the possibility to use internal serializer-deserializer such as a serial transceiver. This approach is very useful in interfacing different devices. The idea is to daisy-chain the output of one combined module to one of the inputs of the next combined module. I've created a module that calls on two other modules-a 2:1 mux and a D-flip-flop (both of which compile and simulate-correctly-individually). In this post, we analyzed the VHDL code for a parallel to serial converter. I need to implement a serial to parallel converter.